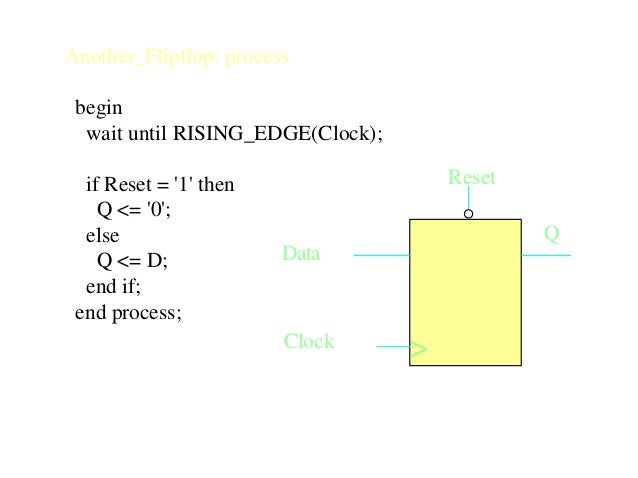

What’s the difference between arithmetic shift and logical shift?Ī logical shift means that the new bits are replaced with zeros. And much more history can be found here: The shift and rotate operators sll, roretc are for vectors of boolean, bitor std_ulogic, and can have interestingly unexpected behaviourin that the arithmetic shifts duplicate the end-bit even when shifting left. Why do arithmetic shifts duplicate the end bit? A logical shift means that the new bits are replaced with zeros. There are two types of shifts: Logical and Arithmetic. Shifting is a quick way to create a Shift Register. The functions take two inputs: the first is the signal to shift, the second is the number of bits to shift.

Performing shifts in VHDL is done via functions: shift_left() and shift_right().

#Vhdl shift left how to#

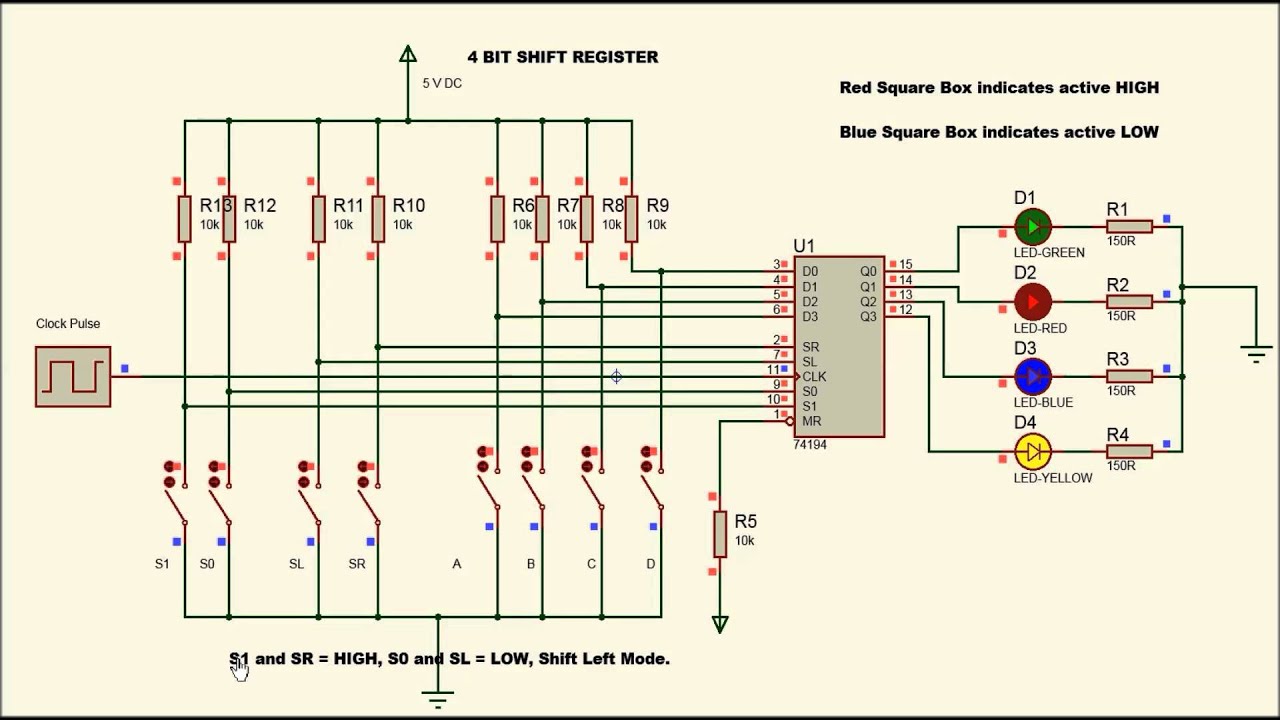

How to do shift left and shift right in VHDL? The division by 32.768 is simply implemented by right shift of 15 positions. A/B you have to simply implement A * (1/B). The trick is to use a multiplication instead of a division. There is a simple trick that can be used if you need to divide a number by a constant. The registers have two modes of operation: parallel (broadside) load, and shift (in the direction QA and QD).

#Vhdl shift left serial#

These 4-bit registers feature parallel inputs, parallel outputs, J-K serial inputs, shift/load control input, and a direct overriding clear.

#Vhdl shift left code#

The above code checks that the inputted mantissa is in the formĠ1.xxxxxxxxx. SUBTRACT ONE FROM THE EXPONENT AND OUTPUT SHIFTED MANTISSAĮxponentNORM(0) := exponentIN(0) xor exponentNEGONE(0) xor '1' ĮxponentCARRY(0) := (exponentIN(0) and exponentNEGONE(0)) or ('1' and (exponentIN(0) xor exponentNEGONE(0))) ĮxponentNORM(i) := exponentIN(i) xor exponentNEGONE(i) xor exponentCARRY(i-1) ĮxponentCARRY(i) := (exponentIN(i) and exponentNEGONE(i)) or (exponentCARRY(i-1) and (exponentIN(i) xor exponentNEGONE(i))) MantissaHEAD := mantissaIN(47 downto 46) -First bits of mantissa Variable exponentCARRY : std_logic_vector(7 downto 0)

Variable exponentNEGONE : std_logic_vector(7 downto 0) := "11111110" Variable exponentONE : std_logic_vector(7 downto 0) := "00000001" Variable exponentNORM : std_logic_vector(7 downto 0) Variable mantissaHEAD : std_logic_vector(1 downto 0) Process(enableIN,signIN,exponentIN,mantissaIN) MantissaIN : in std_logic_vector(47 downto 0) The code that I have so far is this library ieee ĮxponentIN : in std_logic_vector(7 downto 0) Part of this is left or right shifting a 48 bus which represents the mantissa output. I was put in charge of the re-normalization.

#Vhdl shift left 32 bit#

I am designing a 32 bit floating point pipelined and synthesizable adder/multiplier as part of group for a class in school.

0 kommentar(er)

0 kommentar(er)